Verification Continuum<sup>™</sup> UVM Register Abstraction Layer Generator User Guide

R-2020.12, December 2020

## **Copyright Notice and Proprietary Information**

© 2020 Synopsys, Inc. All rights reserved. This Synopsys software and all associated documentation are proprietary to Synopsys, Inc. and may only be used pursuant to the terms and conditions of a written license agreement with Synopsys, Inc. All other use, reproduction, modification, or distribution of the Synopsys software or the associated documentation is strictly prohibited.

#### **Third-Party Software Notices**

VCS® and configurations of VCS includes or is bundled with software licensed to Synopsys under free or open-source licenses. For additional information regarding Synopsys's use of free and open-source software, refer to the third\_party\_notices.txt file included within the *<install\_path>/doc* directory of the installed VCS software.

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### Trademarks

Synopsys and certain Synopsys product names are trademarks of Synopsys, as set forth at http://www.synopsys.com/company/legal/trademarks-brands.html. All other product or company names may be trademarks of their respective owners.

#### Free and Open-Source Software Licensing Notices

If applicable, Free and Open-Source Software (FOSS) licensing notices are available in the product installation.

#### **Third-Party Links**

Any links to third-party websites included in this document are for your convenience only. Synopsys does not endorse and is not responsible for such websites and their practices, including privacy practices, availability, and content.

www.synopsys.com

## Contents

#### 1. Code Generation

| Generating a RAL Model1-1                 |

|-------------------------------------------|

| Options                                   |

| Embedding Enums in Field Classes          |

| Splitting Model into Separate Files 1-5   |

| Splitting Model into Separate Packages    |

| Generating Model for Top-Level Block Only |

| Prunable Register Model 1-12              |

| Understanding the Generated Model         |

| Fields                                    |

| Registers                                 |

| Arrays                                    |

| Register Files 1-18                       |

| Virtual Registers                         |

| Memories                                  |

| Blocks                                    |

| Systems                                   |

Inserting User-Defined Code Inside the Generated RAL Model Classes 1-27

| 2. | Register and Memory Specification                                   |

|----|---------------------------------------------------------------------|

|    | Systems, Blocks, Registers, and Fields                              |

|    | Reusability and Composition                                         |

|    | Naming                                                              |

|    | Hierarchical Descriptions and Composition                           |

|    | Arrays and Register Files                                           |

|    | Support for Different Reset Values in Register Arrays for RALF 2-13 |

|    | Virtual Fields and Virtual Registers2-14                            |

|    | Multiple Physical Interfaces                                        |

|    | Special Registers                                                   |

|    | Indirect Indexed Registers 2-20                                     |

|    | Unimplemented Registers 2-25                                        |

|    | Aliased Registers                                                   |

|    | Banked Registers                                                    |

|    | Shared Registers 2-38                                               |

|    | Sparse Register Arrays 2-39                                         |

|    | Modeling Non-Standard Behavior of Registers                         |

|    | Accessing Registers Based on Index in a regfile 2-42                |

|    |                                                                     |

#### 3. Generated Back-doors

| Arrays |  |  |  |  | . 3- | 3 |

|--------|--|--|--|--|------|---|

|--------|--|--|--|--|------|---|

| %d Format Specifier 3-4                                                 |

|-------------------------------------------------------------------------|

| [%d] Format Specifier 3-5                                               |

| [%d:%d] Format Specifier 3-6                                            |

| [%g] Format Specifier 3-8                                               |

| Backdoor Support for VHDL or Mixed Language Designs 3-10                |

| Scoping Backdoor Classes to a SV Package                                |

| Target Structures                                                       |

| Support for Value Inversion in Backdoor Code                            |

| Support for Field Association with Register Backdoor Specification 3-24 |

| Support for Register Array Index in Field Paths                         |

| Support for Active Monitoring Logic                                     |

|                                                                         |

#### 4. Functional Coverage Model

| Predefined Functional Coverage Models | 3  |

|---------------------------------------|----|

| Register Bits 4-                      | -4 |

| Address Map 4-                        | -5 |

| Field Values 4-                       | -6 |

| RALF Cover Attribute                  | 11 |

5. Randomizing Field Values

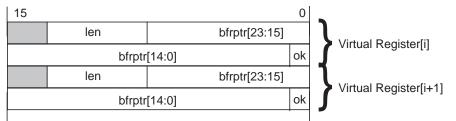

| 6. Generating RALF and UVM Register Model from IP-XACT |                              |       |  |  |  |

|--------------------------------------------------------|------------------------------|-------|--|--|--|

|                                                        | Definition of IP-XACT Schema | . 6-2 |  |  |  |

|    | RALF File Description Mechanism6-2                                                                         |

|----|------------------------------------------------------------------------------------------------------------|

|    | Supported IP-XACT Schema6-5                                                                                |

|    | Generic RALF Features and IP-XACT Mapping                                                                  |

|    | Access Types.6-13Reserved and Parameters Attributes.6-17Reset/Mask for Register6-17Volatile Construct.6-19 |

|    | Vendor Extensions                                                                                          |

|    | Limitations of IP-XACT to RALF Feature Mapping6-32                                                         |

| 7. | UVM Register C++ Interface                                                                                 |

|    | C++ Register Model                                                                                         |

|    | Instantiating the Register Model                                                                           |

|    | Retrieving IDs of All the Registers in a Block/System7-6                                                   |

|    | Co-Simulation Execution Timeline                                                                           |

| Ар | pendix A. RALF Syntax                                                                                      |

|    | Grammar Notation                                                                                           |

|    | Reserved Words A-2                                                                                         |

|    | Useful Tcl Commands                                                                                        |

|    | RALF Construct Summary                                                                                     |

| registerA-                                                       | -11 |

|------------------------------------------------------------------|-----|

| regfileA-                                                        | -18 |

| memory A-                                                        | -23 |

| virtual register A-                                              | -26 |

| blockA-                                                          | -28 |

| system                                                           | -38 |

| Appendix B. Limitations in Code Generation for UVM Register Mode | əl  |

| FieldsB-                                                         | 1   |

| Volatility B-                                                    | -1  |

| has_resetB                                                       | -2  |

| individually_accessibleB·                                        | -2  |

| soft_resetB·                                                     | -2  |

| set_compare()                                                    | -2  |

| MemoriesB-                                                       | 3   |

| Coverage B-                                                      | -3  |

| RegistersB-                                                      | 3   |

| UVM_REG_FIFOs B-                                                 | -3  |

| REGISTER CALLBACKS B-                                            | -3  |

# 1

# **Code Generation**

Once a description of available registers and memories in a design is available, ralgen can automatically generate the UVM RAL abstraction model for these registers and memories. Test cases, firmware, device drivers, and DUT configuration code use this model to access the registers and memories through an object-oriented abstraction layer. Predefined tests also use this model to verify the functional correctness of the registers and memories.

This section consists of the following subsections:

- "Generating a RAL Model"

- "Understanding the Generated Model"

- "Inserting the User-Defined Code Inside the Generated RAL Model Classes"

- "Specifying Map Name in Single Domain Blocks"

Feedback

## **Generating a RAL Model**

To generate a RAL model, use the following command:

% ralgen [options] -t topname -I dir -uvm {filename.ralf}

#### Where:

#### -t topname

Specifies the name of the top-level block or system description in the RALF file that entirely describes the design under verification.

-uvm

Specifies UVM as the implementation methodology for the generated code. The RAL model for the entire design is generated in a file named ral\_topname.sv in the current working directory.

-I dir

Specifies an optional list of directories that ralgen searches for sourced Tcl files.

filename.ralf

Specifies the name of the files containing the RALF description. Although the .ralf extension is not required, Synopsys recommends you to specify it. However, for multiple files one toplevel RALF file is specified that should include all the other files through the include Tcl option. For example, in the top RALF file, source bottom.ralf should be present.

#### Options

The following options are available:

-all\_fields\_rand

Allows you to configure all the writable fields as rand (is\_rand\_bit is set to 1) without requiring the constraint block to be specified. The generated code only marks fields, which have constraints defined with them as rand by default.

-b

Generates the back-door access code for those registers and memories where a complete hdl\_path is specified.

-B, gen\_byte\_addr

Generates RAL model with byte-level address granularity.

-с а

Generates the "Address Map" functional coverage model. You may specify the -c option multiple times.

-c b

Generate the "Register Bits" functional coverage model. You may specify the -c option multiple times.

-c f

Generates the "Field Values" functional coverage model. You may specify the -c option multiple times.

-C S

Generates separate bins for read-only bits to read both 1 and 0 for read-only registers for ralgen-generated bit-level coverage. Specifying the -c b option alongside the -c s option results in an error.

-e

Generates empty constraint blocks for every abstract class.

-f <filename>

Specifies all ralgen options within a file.

-flds\_out\_reg all | none | no\_uniq

Controls the field handle generation in blocks.

all - Generates all field handles in blocks (same as not providing -flds\_all\_reg).

none - Generates no field handles in blocks.

no\_uniq - Generates no field handles for uniquely named fields in blocks.

-gen\_html

Generates the RAL model and its HTML UVM document. Its related files are dumped in the ral\_top\_path\_name\_doc directory. An error appears, if this option is specified without the -uvm option.

-no\_vif\_self\_inst

Omits the generation of the initial block inside the interface for self registering. This option can only be used with the -gen\_vif\_bkdr option.

-top\_macro <string\_which\_overrides\_default\_macro>

Allows you to use a different macro instead of name\_TOP\_PATH to specify the absolute path to the instance of the DUT that corresponds to the RAL model.

#### **Embedding enum in Field Classes**

If an enum is present in a field, ralgen creates a class containing that enum, but that class is not used and the enum is not embedded in the field class.

ralgen is enhanced and the <code>-embed\_enum\_in\_flds</code> option is provided to allow embedding an enum in the field class itself. If this option is used, ralgen embeds an enum in a class extending from the <code>uvm\_reg\_field</code> class and creates the corresponding field instance using this <code>uvm\_reg\_field</code> extension class. For example, consider the following RALF code snippet:

```

block b1 {

bytes 1;

register r {

bytes 1;

field WDT_EN @'h5 {

bits 1;

reset 'h0;

access rw;

enum { ENABLE = 1, DISABLE = 0 };

}

}

```

In the code snippet, the field class is extended from the uvm\_reg\_field class and used in a register as follows:

```

class ral_fld_b1_r_WDT_EN extends uvm_reg_field;

`uvm_object_utils(ral_fld_b1_r_WDT_EN)`

function new(string name = "WDT_EN");

super.new(name);

endfunction : new

typedef enum bit[0:0] {

ENABLE = 1,

DISABLE = 0

} WDT_EN_values;

endclass : ral_fld_b1_r_WDT_EN

class ral_reg_b1_r extends uvm_reg;

rand ral_fld_b1_r_WDT_EN WDT_EN;

function new(string name = "b1_r");

super.new(name, 8,build_coverage(UVM_NO_COVERAGE));

endfunction: new

virtual function void build();

this.WDT_EN =

```

Feedback

```

ral_fld_bl_r_WDT_EN::type_id::create("WDT_EN",,get_full_na

me());

this.WDT_EN.configure(this, 1, 5, "RW", 0, 1'h0, 1, 1,

1);

endfunction: build

`uvm_object_utils(ral_reg_b1_r)

endclass : ral_reg_b1_r

```

#### **Splitting the Model Into Separate Files**

Instead of generating a complete model into a single file named ral\_topblkname.sv, you can optionally split the generated register model into individual files, one per block. The individual files can then be used in the verification environment of the individual blocks.

#### **Command-Line Option**

-F

When specified, the option saves the generated model in separate files.

## **Specification**

For the top-level block, it instantiates each sub-block, which is specified in the input RALF file(s). The corresponding register abstraction model is generated in a separate file named ral\_blkname.sv.

The file contains all the class declarations implied by the block specification. This includes register type, register file type, and the block type classes.

Feedback

Register and register file types specified outside of a block specification is surrounded by pre-processor guard statements.

The `include statements include the files containing the generated model for the blocks instantiated in the block for the current file are generated at the top of the block model file. The entire content of the file is embedded in a pre-processor guard.

## Example

Consider the following (partial) RALF file:

```

register R0 {...};

block B1 {

register R0;

register R1 {...};

}

block B2 {

register R0;

register R1 {...};

}

system sys {

bytes 16;

block B1;

block B2

}

ralgen -uvm -t sys sys.ralf -F

```

It generates the required (partial) class declarations in the following files:

```

ral_B1.sv:

```

```

`ifndef RAL_B1__SV

`define RAL_B1__SV

`ifndef RAL_R0__TYP

`define RAL_R0__TYP

class ral_R0 ...;

`endif

class ral_B1_R1 ...;

class ral_B1 ...;

`endif

ral_B2.sv:

`ifndef RAL_B2__SV

`define RAL_B2__SV

`include "ral_B1.sv"

`ifndef RAL_R0__TYP

`define RAL_R0__TYP

class ral_R0 ...;

`endif

class ral_B2_R1 ...;

class ral_B2 ...;

`endif

```

## Splitting the Model into Separate Packages

Instead of generating a complete model into a single file named ral\_topblkname.sv, the generated register model can be optionally split into individual files, one per block, with all blockrelated type declarations encapsulated in a package. The individual files can then be compiled separately and used in the verification environment of the individual blocks.

## **Command-Line Option**

-P

When specified, the option saves the generated model in separate packages and in separate files.

#### **Specification**

- A warning appears if -F option is specified with the -P option.

- The -P option takes the precedence. ٠

- For the top-level block, and each sub-block it instantiates, ۲ specified in the input RALF file(s), the corresponding register abstraction model is generated in a separate packaged named ral\_blkname\_pkg in a separate file named ral blkname pkg.sv.

- The package contains all the class declarations implied by the ۲ block specification. This includes register type, register file type, and the block type classes.

- Register and register file types specified outside of a block ۲ specification is included in the package without special treatment.

- Import statements to import the declarations from the packages containing the generated model for the blocks instantiated in the block for the current package are generated at the top of the package.

- The entire content of the file is embedded in a pre-processor guard.

- The list of vlogan commands required to compile the packages in the correct order is generated into the ral\_topblkname.compile file name and is duplicated on the standard output.

#### Example

Consider the following (partial) RALF file:

```

register R0 {...};

block B1 {

register R0;

register R1 {...};

}

block B2 {

register R0;

register R1 {...};

}

system sys {

bytes 16;

block B1;

block B2;

}

ralgen -uvm -t sys sys.ralf -P

```

Generates the required (partial) class and package declarations in the following files:

ral\_B1\_pkg.sv:

```

`ifndef RAL_B1_PKG__SV

`define RAL_B1_PKG__SV

package ral_B1_pkg;

import uvm_pkg::*;

class ral_R0 ...;

class ral_B1_R1 ...;

class ral_B1 ...;

endpackage

`endif

ral B2 pkq.sv:

`ifndef RAL_B2_PKG__SV

`define RAL_B2_PKG__SV

package ral_B2_pkg;

import uvm_pkg::*;

import ral_B1_pkg::*;

class ral_R0 ...;

class ral_B2_R1 ...;

class ral_B2 ...;

endpackage

`endif

ral_B2.compile:

vlogan -sverilog ral_B1_pkg.sv

vlogan -sverilog ral_B2_pkg.sv

```

## Generating the Model for Top-Level Block Only

Instead of generating a complete model which includes all the blocks instantiated in the top-most block, only the model for the top-most block can be optionally generated. It is assumed that the register models for the instantiated blocks are previously generated. This allows the SoC team to generate the register model for the SoC only and to inherit the register models for the instantiated IPs from the IPlevel verification environments.

Note:Individually generated register models must use the same packaging approach to be compatible. For example, the model for a block generated without a package (using the -T option) is not compatible with the model for a block generated within a package (using the -P option).

If you need to generate a register model for multiple blocks, each is generated through a separate invocations of ralgen with each block specified as the topmost block in turn.

## **Command-Line Option**

-T

When specified, the option generates the register model for the specified topmost block.

#### Specification

- It is necessary to specify the -F option or the -P option when specifying the -T option.

- Only the file corresponding to the specified topmost block is generated.

Feedback

#### Example

Consider the following (partial) RALF file:

```

register R0 {...};

block slave1 {

register R0;

register R1 {...};

}

block slave2 {

register R0;

register R1 {...};

}

system sys {

bytes 16;

block slave1;

block slave2;

}

```

It generates the required (partial) class and package declarations in the following files:

```

ralgen -uvm -t sys slave_two_block.ralf -F -T

will generate ral_sys.sv

ralgen -uvm -t slave1 slave_two_block.ralf -F -T

will generate ral_slave1.sv

ralgen -uvm -t slave2 slave_two_block.ralf -F -T

will generate ral_slave2.sv

```

## **Prunable Register Model**

Large SoCs contain multiple thousands of registers. Depending on the way the registers are modeled, this may cause the generation of multiple thousands of classes declarations and the instantiation of several tens of thousands of class instances.

Most SoC-level tests do not need a complete register model. They only need the portions of the model that are used by the test case. To reduce compile-time and run-time resources, it should prune the register model of all unnecessary block-level register models.

#### **Command-Line Option**

#### +prunable

When specified, the option helps the generated model to include directives to optionally prune the register model at compile time.

#### **Specification**

- It is necessary to specify the -F option or the -P option when specifying the +prunable option.

- For each block instantiated in the register model contained in the generated file, the corresponding `include or import directive is embedded in a pre-processor guard.

- For each block instantiated in the register model contained in the generated file, the corresponding block instance class property is embedded in the same pre-processor guard that guards the `include or import statement for that block.

- Any statement referring to a block instance class property is embedded in the same pre-processor guard that guards the `include or import statement for that block.

- The pre-processor symbol guarding the `include or import statement and the class property for an instantiated block is named RAL\_PRUNE\_BLKNAME.

- By default, none of the pre-processor guard symbols is defined.

#### Example

Consider the following (partial) RALF file:

```

register R0 {...};

block B1 {

register R0;

register R1 {...};

}

block B2 {

register R0;

register R1 {...};

}

system sys {

bytes 16;

block B1;

block B2;

}

ralgen -uvm -t sys sys.ralf +prunable -P

```

It generates the required (partial) prunable class and package declarations in the following files:

#### ral\_B1\_pkg.sv:

```

`ifndef RAL_B1_PKG__SV

`define RAL B1 PKG SV

package ral_B1_pkg;

import uvm_pkg::*;

class ral_R0 ...;

class ral_B1_R1 ...;

class ral_B1 ...;

endpackage

`endif

ral_B2_pkg.sv:

`ifndef RAL_B2_PKG__SV

`define RAL_B2_PKG__SV

package ral_B2_pkg;

import uvm_pkg::*;

`ifndef RAL PRUNE B1

import ral_B1_pkg::*;

`endif

class ral R0 ...;

class ral_B2_R1 ...;

class ral_B2 extends uvm_reg;

rand ral_R0

R0;

rand ral_B2_R1 R2;

`ifndef RAL_PRUNE_B1

rand ral_B1 b1;

`endif

. . .

function void build();

`ifndef RAL PRUNE B1

b1 = ...;

`endif

endfunction

endclass

endpackage

`endif

```

## **Understanding the Generated Model**

The generated abstraction model is a function of the RALF description used to generate it. Therefore, understanding how the generation process works helps you to use the generated model based on the knowledge of the RALF description.

The generated abstraction model is described using a bottom-up approach, in the order in which the classes are generated and then compiled. If you prefer to read a top-down description, simply read the following sections ("Fields", "Registers", "Register Files", "Virtual Registers", "Memories", "Blocks", and "Systems") in the reverse order.

Note:

By default, the data in the register or memory access routines is two-state data. The UVM\_REG\_4STATE\_DATA macro allows you to get the four-state data in the register or memory access routines and controls the definition of the uvm\_reg\_data\_t data type.

#### **Fields**

No abstraction class is generated for a field definition. Instead, each field is modeled by an instance of the uvm\_ral\_field class.

The instance of that class is stored in a property of the class modeling the register that instantiates it and the block that instantiates the register.

#### Registers

An abstraction class is generated for each register definition:

- For each independently defined register named regnam, there is a class named ral\_reg\_regnam

- For each register named regnam defined inline in the specification of a block named blknam, there is a class named ral\_reg\_blknam\_regnam

- For each register named regnam defined inline in the specification of a register file named filnam in a block named blknam, there is a class named ral\_reg\_blknam\_filnam\_regnam

In all cases, the register abstraction class is derived from the uvm\_reg class.

All virtual methods defined in the uvm\_reg class are overloaded in the register model class. Each virtual method is overloaded to implement the register-specific behavior of the register as defined in the RALF description. No new methods are added to the register abstraction class.

As shown in Example 1-1, the register abstraction class contains a class property for each field it contains. The name of the property is the name of the field. There are no properties for unused or reserved fields.

Example 1-1 Register Model Class for Register in Example A-5

```

class ral_reg_CTRL extends uvm_ral_reg;

uvm_ral_field TXE;

uvm_ral_field RXE;

uvm_ral_field PAR;

uvm_ral_field DTR;

uvm_ral_field CTS;

...

endclass: ral_reg_CTRL

```

Instances of this class are found in the block abstraction class for the blocks instantiating this register.

#### Arrays

If a register contains any field array, the class property for the field array is declared as a fixed sized array in the corresponding register abstraction class. Consider the following example:

Example 1-2 Array Specifications and Corresponding Model

```

register r {

bytes 1;

field f[8] {

bits 1;

}

}

Its corresponding abstraction model is as follows:

```

```

class ral_reg_b_r extends uvm_ral_reg;

rand uvm_ral_field f[8];

...

endclass: ral_reg_b_r

```

## **Register Files**

An abstraction class is generated for each register file definition. For each register file named filnam defined inline in the specification of a block named blknam, there is a class named ral\_regfile\_blknam\_filnam. The register abstraction class is not derived from the uvm\_blk\_filnam base class and is a container for the registers instantiated in the register file.

The register file container class contains a class property for each register it contains. For example:

Example 1-3 Register File Specification and Corresponding Model

```

block dma_ctrl {

regfile chan {

register src {

field addr { ... }

}

register dst {

field addr { ... }

}

register count {

field n_bytes { ... }

}

register ctrl {

field TXE { ... }

field BSY { ... }

}

}

}

```

Its corresponding abstraction model is as follows:

```

class ral_regfile_dma_ctrl_chan;

ral_reg_dma_ctrl_chan_src src;

uvm ral field

src addr;

ral_reg_dma_ctrl_chan_dst dst;

uvm ral field

dst addr;

ral_reg_dma_ctrl_chan_count count;

n_bytes, count_n_bytes;

uvm ral field

uvm_ral_field

TXE, ctrl_TXE;

uvm_ral_field

BSY, ctrl_BSY;

. . .

endclass: ral_reg_dma_ctrl_chan

```

Instances (usually arrays of instances) of this class are found in the block abstraction class for the blocks instantiating this register file.

#### **Virtual Registers**

An abstraction class is generated for each virtual register array definition. For each independently-defined virtual register array named vregnam, there is a class named ral\_vreg\_vregnam. For each virtual register array named vregnam defined inline in the specification of a block named blknam, there is a class named ral\_vreg\_blknam\_vregnam. In both cases, the virtual register array abstraction class is derived from the uvm\_vreg class. A single abstraction class is used for all virtual registers in the array.

All virtual methods defined in the uvm\_ral\_vreg class are overloaded in the virtual register array abstraction class. Each virtual method is overloaded to implement the register-specific behavior of the virtual register array as defined in the RALF description. No new methods are added to the virtual register array abstraction class. As shown in Example 1-4, the virtual register array abstraction class contains a class property for each virtual field it contains. The name of the property is the name of the field. There are no properties for unused or reserved fields, and unlike register arrays, a single instance of the virtual register array abstraction class is used to model the complete virtual register array.

Example 1-4 Virtual Register Abstraction Class

```

block blk1 {

memory ram0 { ... }

virtual register dma[256] ram0@0x0000 {

field len { ... }

field bfrptr { ... }

field ok { ... }

}

}

```

Its corresponding abstraction model is as follows:

```

class ral_vreg_blk1_dma extends uvm_ral_vreg;

uvm_ral_vfield len;

uvm_ral_vfield bfrptr;

uvm_ral_vfield ok;

...

endclass: ral_vreg_blk1_dma

class ral_block_blk1 extends uvm_reg_block;

uvm_ral_mem ram0;

ral_vreg_blk1_dma dma;

...

endclass: ral_block_blk1

```

A single instance (not an array of instance) of this class is found in the block abstraction class for the blocks instantiating a virtual register array.

#### **Memories**

An abstraction class is generated for each memory definition. For each independently defined memory named memnam, there is a class named ral\_mem\_memnam. For each memory named memnam defined inline in the specification of a block named blknam, there is a class named ral\_mem\_blknam\_memnam.

In both cases, the memory abstraction class is derived from the uvm\_ral\_mem class.

All virtual methods defined in the uvm\_ral\_mem class are overloaded in the memory abstraction class. Each virtual method is overloaded to implement the memory-specific behavior of the memory as defined in the RALF description. No new methods are added to the memory abstraction class.

As shown in Example 1-5, the memory abstraction class contains no additional class properties.

Example 1-5 Memory Abstraction Class for Memory in Example A-10

class ral\_mem\_ROM extends uvm\_ral\_mem;

...

endclass: ral\_mem\_ROM

Instances of this class are found in the block abstraction class for the blocks instantiating this memory.

#### **Blocks**

An abstraction class is generated for each block definition. For each independently defined block named blknam, there is a class named ral\_block\_blknam. For each block named blknam defined inline in the specification of a system named sysnam, there is a class named ral\_block\_sysnam\_blknam. In both cases, the block abstraction class is derived from the uvm\_reg\_block class.

All virtual methods defined in the uvm\_reg\_block class are overloaded in the block abstraction class. Each virtual method is overloaded to implement the block-specific behavior of the block as defined in the RALF description. No new methods are added to the block abstraction class.

As shown in Example 1-6 and Example 1-7, the block abstraction class contains a class property for each register and register file it contains. The name of the register or register file property is the name of the register or file. The block abstraction class also contains one or two class properties for each field it contains. The name of each field property is the name of the field (if unique within the register) and the name of the register concatenated with the name of the field, respectively. There are no properties for unused or reserved fields.

In certain situations, it may be necessary to:

• Not generate any field properties outside the register class.

or

• Generate field properties with register name pre-fixed to field name, while leaving out field properties with unique names.

Feedback

You can control the field generation using the following commandline option:

-flds\_out\_reg all | none |no\_uniq

where,

all - This is default. It implies the current behavior.

${\tt none}$  - This specifies that no field handles are generated outside the register class.

${\tt no\_uniq}$  - This specifies that no field handles are generated for unique names outside the register class.

#### Important:

It is preferable that field names be unique across blocks. Therefore, each field has a property with the same name in the block abstraction class that instantiates them. If you move the field to another physical register, you can use this uniquely-named field property to reduce testbench maintenance. If you use the name that is prefixed with the register name, you must modify testbenches if the field is relocated to another physical register.

Example 1-6 Block Abstraction Class for Block in Example A-11

```

class ral_block_uart extends uvm_reg_block;

ral_reg_CTRL CTRL;

uvm_ral_field TXE, CTRL_TXE;

uvm_ral_field RXE, CTRL_RXE;

uvm_ral_field PAR, CTRL_PAR;

uvm_ral_field DTR, CTRL_DTR;

uvm_ral_field CTS, CTRL_CTS;

ral_mem_tx_bfr tx_bfr;

...

endclass: ral_block_uart

```

Example 1-7 Block Abstraction Class for Block in Example A-13

```

ral_block_bridge extends uvm_reg_block;

ral_reg_flags pci_flags;

uvm_ral_field pci_flags_cts;

uvm_ral_field pci_flags_dtr;

ral_reg_data_xfer to_ahb;

uvm_ral_field to_ahb_data;

ral_reg_data_xfer frm_ahb;

uvm_ral_field frm_ahb_data;

ral_reg_flags ahb_flags;

uvm_ral_field ahb_flags_cts;

uvm_ral_field ahb_flags_dtr;

ral_reg_data_xfer to_pci;

uvm_ral_field to_pci_data;

ral_reg_data_xfer frm_pci;

uvm_ral_field frm_pci_data;

...

endclass: ral_block_bridge

```

Instances of this class are found in the system model class for the systems instantiating this block.

#### Arrays

If a block contains a register array or register file array, the class property for the register array or register file array is declared as a fixed-sized array to the corresponding register abstraction class or the register file container class. Similarly, the field properties for the fields contained in the register array are declared as a fixed-sized array of uvm\_ral\_field classes.

Example 1-8 Array Specifications and Corresponding Model

```

block b1 {

register r1[32] {

field f1 { ... }

}

regfile rf[16] {

register r1 {

field f1 { ... }

}

register r2[4] {

field f1 { ... };

}

}

}

```

Its corresponding abstraction model is as follows:

```

class ral_regfile_b1_rf;

ral_reg_b1_rf_r1 r1;

uvm_ral_field r1_f1;

ral_reg_b1_rf_r2 r2[4];

uvm_ral_field f2_f1[4];

...

endclass: ral_regfile_b1_rf

class ral_block_b1 extends uvm_reg_block;

ral_reg_b1_r1 r1[32];

uvm_ral_field f1[32], r1_f1[32];

ral_regfile_b1_rf rf[16]

...

endclass: ral_block_b1

```

#### Systems

An abstraction class is generated for each system definition. For each independently defined system named sysnam, there is a class named ral\_sys\_sysnam. For each subsystem named subnam defined inline in the specification of a system named sysnam, there is a class named ral\_sys\_sysnam\_subnam.

In both cases, the system abstraction class is derived from the uvm\_reg\_block class as in the case of the abstraction classes generated for each 'block' definition (for details, see uvm\_reg\_block in the UVM1.0 Reference Guide).

All virtual methods defined in the uvm\_reg\_block class are overloaded in the system abstraction class. Each virtual method is overloaded to implement the system-specific behavior of the system as defined in the RALF description. No new methods are added to the system abstraction class.

As shown in Example 1-9 and Example 1-10, the system abstraction class contains a class property for each block and subsystem it contains. The name of the block or subsystem property is the name of the block or system. For blocks with multiple domains, the name of the blocks and subsystems are also available prefixed with the domain name.

#### Example 1-9 System Abstraction Class for Example A-14

```

class ral_sys_SoC extends uvm_reg_block;

ral_block_uart uart0;

ral_block_uart uart1;

...

endclass: ral_sys_SoC

```

Feedback

Example 1-10 System Abstraction Class for Example A-15

```

class ral_sys_SoC extends uvm_reg_block;

ral_block_uart uart0, ahb_uart0;

ral_block_uart uart1, ahb_uart1,

ral_block_bridge ahb_br;

ral_block_bridge pci_br;

...

endclass: ral_sys_SoC

```

## Inserting the User-Defined Code Inside the Generated RAL Model Classes

You can insert the user-defined code to the generated RAL model classes using the user\_code construct, as follows:

```

user_code lang=sv [(new)]

{

// Any kind/syntax of user code can be added here

}

```

If the optional (new) argument is specified, it indicates that user\_code is appended/inlined to/in the corresponding (RAL Model) class body of the build method. In case of a virtual register, user\_code is inlined in the virtual register constructor.

If the new argument is not specified, user\_code is not inlined in the build method code. By default, it is located outside the constructor body (but inside the class), thus, opening up options of adding new data members, functions, or task definitions and so on in the generated RAL model classes.

You can also use the user\_code construct as an optional property in the definition or specification of a RALF register, virtual register, memory, regfile, block, or system as shown in the example below. Note:

You can specify more than one RALF user\_code in the definition or specification of a RALF register, virtual register, memory, regfile, block, or system. The contents are concatenated in the generated RAL model class in the same sequence as their corresponding occurrence in the RALF file.

#### Example 1-11 RALF Description With User Code

```

block b {

bytes 1

user_code lang=SV {

// Any block level code can come here.

}

register r {

bytes 1

field f

user_code lang=SV (new) {

// Any register level build method code can come here.

}

}

}

```

This example generates the following RAL classes with user\_code inlined appropriately:

```

class ral_reg_b_r extends uvm_reg;

rand uvm_reg_field f;

function new(string name = "b_r");

super.new(name,

8,build_coverage(UVM_NO_COVERAGE));

endfunction: new

virtual function void build();

this.f =

uvm_reg_field::type_id::create("f",,get_full_name());

this.f.configure(this, 1, 0, "RW", 0, 1'h0, 0, 0, 1);

//////

// User Code - Begin

//////

// Any register level build method code can come here.

```

```

//////

// User Code - End

//////

endfunction: build

`uvm_object_utils(ral_reg_b_r)

endclass : ral_reg_b_r

class ral_block_b extends uvm_reg_block;

rand ral_reg_b_r r;

rand uvm_reg_field r_f;

rand uvm req field f;

//////

// User Code - Begin

//////

// Any block level code can come here.

//////

// User Code - End

//////

function new(string name = "b");

super.new(name, build_coverage(UVM_NO_COVERAGE));

endfunction: new

virtual function void build();

this.default_map = create_map("", 0, 1,

UVM_LITTLE_ENDIAN, 0);

this.r =

ral_reg_b_r::type_id::create("r",,get_full_name());

this.r.configure(this, null, "");

this.r.build();

this.default_map.add_reg(this.r,

`UVM_REG_ADDR_WIDTH'h0, "RW", 0);

this.r_f = this.r.f;

this.f = this.r.f;

endfunction : build

`uvm_object_utils(ral_block_b)

endclass : ral_block_b

```

#### Arrays

If a system contains a block array or subsystem array, the class property for the block array or subsystem array is declared as a fixed-sized array of the corresponding block abstraction class or system abstraction class.

```

Example 1-12 System Abstraction Class With Block Array

```

```

class ral_sys_SoC extends uvm_reg_block;

ral_block_uart uart[2]

...

endclass: ral_sys_SoC

```

## Specifying Map Name in Single Domain Blocks

Ralgen supports specifying user-defined map names for a single domain block.

Following RALF syntax can be used within the block construct.

```

default_map_name <identifier>

```

#### Example

The following is a (partial) RALF file:

```

block foo {

```

```

default_map_name my_map

bytes 7

register r2_vh=r2_vh

register r3_vh= r3_vh

registerr2_rec_vh=reg_vec (reg_rec)

register r1=r3[2](reg_ar[%g])

```

Feedback

Following is the generated SystemVerilog code:

```

class ral_block_foo extends uvm_reg_block;

virtual function void build();

this.my_map = create_map("my_map", 0, 7,

UVM_LITTLE_ENDIAN, 0);

this.default_map = this.my_map;

uvm_reg_map my_map;

....

endclass

```

}

## **Register and Memory Specification**

The Register Abstraction Layer File (RALF) is used to specify all the registers and memories in the design under verification. It is used to generate the object-oriented register and memory high-level abstraction layer. The first step in a project is to create a RALF description. Appendix - "RALF Syntax" contains detailed syntax and documentation for the RALF description.

As you add and modify fields, registers, and memories, you can update the RALF description many times during a project. You can then regenerate the abstraction layer multiple times without requiring modifications to the existing environment or tests.

## Systems, Blocks, Registers, and Fields

In RAL, a design is a block or a system of blocks. The smallest functional unit that can be verified is a block. Systems are designs composed of blocks. Systems can also be composed of smaller systems of blocks, called subsystems.

There must be at least one block in a RALF description. The toplevel construct describing the design under verification can be a block or system construct. The top-level block is identified when the RAL code is generated, therefore, a single RALF description may contain descriptions of multiple blocks and systems. The following example shows the RALF description of a design block:

Example 2-1 RALF Description of a Design Block

```

block blk_name {

...

}

```

Systems are composed of subsystems or blocks. Blocks are composed of registers, memories, and sub-blocks. There can be no registers or memories directly in a system. If a design has systemwide registers or memories, they should be described in a named block, for example, system\_wide. The following example shows the RALF description of a system:

#### Example 2-2 RALF Description of a System

```

system sys_name {

...

block blk_name ...

system subsys_name ...

}

```

Registers are composed of fields. Fields are concatenated to form a register, with optional unused bits between fields. A register must contain at least one field. The following example shows the RALF description of registers and memories in a block:

```

Example 2-3 RALF Description of Registers and Memories in a Block

```

```

block blk_name {

...

register reg_name ...

register reg_name ...

memory mem_name ...

}

```

The field is the basic unit of the RAL. Fields are accessed automatically, independent of their location within a register or other fields. Therefore, fields can be moved within or across registers without the need to modify the code that uses them. The following example shows the RALF description of fields in a register:

Example 2-4 RALF Description of Fields in a Register

```

register reg_name {

...

field fld_name ...

field fld_name ...

}

```

## **Reusability and Composition**

RALF descriptions are intended to describe designs that can be arbitrarily combined and reused to create larger designs. A RALF description of a block or subsystem is not required to be aware of the context in which the block or subsystem is going to be used. In RALF descriptions, blocks, and subsystems are described as stand-alone designs. Even if a RALF can describe an entire design inline, as shown in Example 2-5, a description can also instantiate blocks, registers, and fields as required. The granularity of the description is arbitrary and you should plan for it to maximize reuse.

Example 2-5 Inlined RALF Description

RALF descriptions can include other RALF descriptions of smaller designs. Included descriptions can be reused and instantiated to compose the description of a larger design. The following example illustrates how this can be performed:

Example 2-6 Hierarchical RALF Description

```

field fld_name {

...

}

register reg_name {

...

field fld_name ;

}

memory mem_name {

...

```

Register and Memory Specification

```

}

block blk_name {

...

register reg_name;

memory mem_name;

}

system sys_name {

...

block blk_name;

}

```

## Naming

The names of fields, registers, memories, blocks, and systems are important because these names are used to identify their corresponding abstraction class in the RAL abstraction model.

The following naming conventions apply to the names elements within a RALF description:

• Names must not be OV or SV reserved keywords

These names are used as the name of abstraction classes in the generated OV or SV code. Therefore, they cannot be the same as reserved keywords in OV or SV.

• Field names should be unique within a block

Each block abstraction class contains a class property for each field contained in all of its registers, regardless of the specific register where it is located. If unique, the name of the field class property within the block abstraction class is the name of the field. In this case, fields can be moved within or across physical registers without affecting the verification environment or tests. Regardless of field name uniqueness, the block abstraction class contains another field class property referring to each field using the concatenation of the register and field name. See "Registers" section for additional information.

#### Example 2-7 Field Class Properties in a Block Abstraction Class

```

block blk_name {

register reg_name {

field fld1;

field fld2;

}

register xyz {

field fld2;

}

}

Yields:

class ral_block_blk_name extends uvm_reg_block;

...

uvm_ral_field fld1, reg_name_fld1;

uvm_ral_field reg_name_fld2;

...

uvm_ral_field xyz_fld2

endclass

```

• Register names must be unique within a block and field names.

Each block abstraction class contains a class property for each register it contains. The name of the register class property within the block abstraction class is the name of the register and must, therefore, be unique and should be different from field names.

Example 2-8 Register Abstraction Classes in a Block Abstraction Class

```

block blk_name {

register reg_name {

field fld1;

field fld2;

}

}

Yields:

class ral_block_blk_name extends uvm_reg_block;

ral_reg_blk_name_reg_name reg_name;

uvm_ral_field fld1, reg_name_fld1;

uvm_ral_field fld2, reg_name_fld2;

endclass

```

• Memory names must be unique within a block and unique from register names and should be unique from field names.

Each block abstraction class contains a class property for each memory it contains. The name of the memory class property within the block abstraction class is the name of the memory and must, therefore, be unique and different from register names. It should also be different from field names.

Example 2-9 Memory Abstraction Classes in a Block Abstraction Class

```

block blk_name {

register reg_name {

field fld1;

field fld2;

}

memory mem_name;

}

Yields:

class ral_block_blk_name extends uvm_reg_block;

ral_reg_blk_name_reg_name reg_name;

uvm_ral_field fld1, reg_name_fld1;

uvm_ral_field fld2, reg_name_fld2;

ral_mem_blk_name_mem_name mem_name;

```

endclass

• Block and subsystem names must be unique within a system.

Each system abstraction class contains a class property for each block and subsystem it contains. The name of the block and subsystem class property within the system abstraction class is the name of the block or subsystem. Therefore, block and subsystem names must be unique.

• Independently defined names of registers, memories, blocks, and systems must be, respectively, globally unique within a RALF description.

Each independently defined RALF element corresponds to a generated abstraction class in the RALF model (see "Understanding the Generated Model"). The names of these elements are used to generate the name of the corresponding class. Class names must be globally unique in SystemVerilog and OpenVera. Therefore, the names of independently defined registers, memories, blocks, and systems must be globally unique, otherwise they generate identical abstraction class names.

This requirement does not apply to elements defined inline within another definition.

Note:

Instantiated fields, registers, memories, blocks and subsystems can be renamed. With all of these naming requirements, it is very difficult to have reusable RALF descriptions. Descriptions need to know their contexts to ensure uniqueness. Also, it is not possible to describe a design that contains multiple instances of the same block. Any element of a RALF description can be renamed when instantiated to ensure uniqueness.

Example 2-10 Renaming RALF Elements

```

block blk_name {

...

}

system sys_name {

...

block blk_name=blk1;

block blk_name=blk2;

}

```

## **Hierarchical Descriptions and Composition**

A RAL description can have independently specified registers, memories, blocks, and subsystems. You can instantiate these elements in higher level elements to create complete design descriptions.

When you specify registers, memories, blocks, and subsystems, you also independently and explicitly specify their physical width as a number of bytes. Therefore, a block can be composed of registers and memories of smaller or larger width. Similarly, systems can be composed of blocks of smaller or larger width.

If you instantiate an element in a wider element, the value of the narrower element is justified to the least-significant bit and the most significant bits are padded with zero or truncated.

If you instantiate an element in a narrower element, the value of the wider element is split into the minimum number of narrower values.

You can specify splitting as:

- **Big Endian** The most-significant bits are split into the lower addresses in the narrower address space. A 5-byte wide value of 0x1234567890 is split into three 2-byte narrower values at increasing addresses in the following order: 0x0012, 0x3456, and 0x7890.

- Little Endian The least-significant bits are split into the lower addresses in the narrower address space. A 5-byte wide value of 0x1234567890 is split into three 2-byte narrower values at increasing addresses in the following order: 0x7890, 0x3456, and 0x0012.

- **Big FIFO** All split values are accessed at the same physical address in the narrower address space. The most-significant bits are accessed first. A 5-byte wide value of 0x1234567890 is split into three consecutive 2-byte narrower values at the same address in the following order: 0x0012, 0x3456, and 0x7890.

- Little FIFO All split values are accessed at the same physical address in the narrower address space. The least-significant bits are accessed first. A 5-byte wide value of 0x1234567890 is split into three consecutive 2-byte narrower values at the same address in the following order: 0x7890, 0x3456, and 0x0012.

## **Arrays and Register Files**

Many designs have identical registers or groups of registers located in consecutive memory locations. These registers could be described by explicitly specifying each register, ignoring the fact that they are identical.

Example 2-11 Explicit Specification of Register Arrays

```

register reg_name {

...

}

block blk_name {

...

register reg_name=reg_0;

register reg_name=reg_1;

...

register reg_name=reg_7;

}

```

The repetitive process can be simplified by using the TCL *for-loop* command. Using the for-loop only simplifies the syntactical requirements of the specification. It does not change the RAL model that is ultimately generated.

Example 2-12 Iterated Explicit Specification of Register Arrays

```

register reg_name {

...

}

block blk_name {

...

for {set n 0} {$n < 8} {incr n} {

register reg_name=reg_$n;

}

}</pre>

```

Feedback

The problem with explicitly enumerating consecutive registers is that they have unique names. It is not possible to randomly index or iterate over their RAL model when writing SystemVerilog or OpenVera code that uses these consecutive registers.

Specifying consecutive registers using a register array results in an array being available to be indexed or iterated on at runtime, not just at specification time. See "Arrays" for more details on the code generation process for arrays.

Example 2-13 Specification of Register Arrays

```

register reg_name {

...

}

block blk_name {

...

register reg_name[8];

register regX[5] {

...

}

}

```

A sequence of register arrays locate them in consecutive memory locations. For example, the specification in Example 2-13 results in the following address map: reg\_name[0], reg\_name[1], ... reg\_name[7], regX[0], regX[1], ... regX[4]. If sequences of register groups, or interleaved register arrays are required, then you should a register file array. The specification in Example 2-14 yields the following address map: reg[0].reg\_name, reg[0].X, reg[1].reg\_name, ... reg[4].reg\_name, reg[4].X.

Example 2-14 Specification of Register File Arrays

```

register reg_name {

...

}

block blk_name {

...

```

Register and Memory Specification

```

regfile reg[5] {

register reg_name;

register X {

...

}

}

}

```

## Support for Storing and Retrieving User-Defined Property Values

Ralgen supports specifying user-defined properties that needs to be stored at model build time and you can later retrieve these properties during simulation. These properties can be specified at register field/ register and map level. You can later retrieve these properties using the get methods generated for those properties and use them in sequences. The values that can be stored are integer, strings, queue or combination of these. You can create properties using the following syntax:

```

user_property property_name handle_identifier

<arguments>

```

For each <property\_name> specified, set\_<property\_name> and get\_<property\_name> accessor methods are created by Ralgen. The arguments of these methods correspond to the <handle\_identifier> and <arguments> specified.

Ralgen generates additional file ral\_db.sv which implements the database. For each <property\_name> specified, set\_<property\_name> and get\_<property\_name> access or

methods are created by Ralgen. The arguments of these methods correspond to the <handle\_identifier> and <arguments> specified.

## Example

The following is a (partial) RALF file:

```

block foo {

bytes 4;

block bar @'h0;

user_property stringstringintprop this string1 string2 12

user_property queueprop this {1, 2, arga}

}

```

Following is the generated SystemVerilog code:

```

...

begin

ral_user_prop_db db_h;

db_h = ral_user_prop_db::me();

db_h.map_db.set_stringstringintprop(this, "string1",

"string2",12);

db_h.map_db.set_queueprop(this, "1, 2, arga");

end

...

```

Dumped Database file (ral\_db.sv):

```

package ral_db_pkg;

import uvm_pkg::*;

class idx_container extends uvm_object;

static idx_container me;

int idx;

local function new();

endfunction

static function idx_container get();

if(me == null) begin

```

```

me = new();

end

return me;

endfunction

endclass

typedef struct {

string val1;

string val2;

int val3;

}struct ssi;

class ral_map_db;

struct_ssi stringstringintprop_map[uvm_reg_map];

function void set stringstringintprop(uvm reg map

r, string val1, string val2, int val3);

struct_ssi struct_ssi_;

struct_ssi_.val1 = val1;

struct_ssi_.val2 = val2;

struct ssi .val3 = val3;

stringstringintprop_map[r] = struct_ssi_;

endfunction

function void get_stringstringintprop(uvm_reg_map

r, output string val1, output string val2, output int val3);

{>>{val1,val2,val3}} =

stringstringintprop_map[r];

endfunction

string queueprop_map[uvm_reg_map];

function void set_queueprop(uvm_reg_map r, string

val1);

queueprop_map[r] = val1;

endfunction

function string get_queueprop(uvm_reg_map r);

return queueprop_map[r];

endfunction

endclass

class ral_reg_db;

string bdf_strings1_map[uvm_reg];

function void set_bdf_strings1(uvm_reg r, string

val1);

bdf_strings1_map[r] = val1;

endfunction

function string get_bdf_strings1(uvm_reg r);

return bdf_strings1_map[r];

```

```

endfunction

endclass

class ral_user_prop_db ;

ral_map_db map_db;

ral_reg_db reg_db;

static ral_user_prop_db user_prop_db_class_handle

;

protected function new();

map db = new();

reg_db = new();

endfunction

static function ral_user_prop_db me();

if(user_prop_db_class_handle == null) begin

user_prop_db_class_handle = new();

end

return user_prop_db_class_handle;

endfunction

endclass

```

endpackage

# Support for Different Reset Values in Register Arrays for RALF

RALF syntax supports the case where you have different reset values. The following property allows you to selectively change the reset value:

change\_reset register\_or\_field\_instance\_to\_reset new\_reset\_value

The register or field instance specified cannot be an array itself, it can only be an array element or a simple instance.

This property is supported inside a regfile or block to override the reset value for a specific register or field. This property can also be used for a simple register or field instance which is not an array element.

The following example shows the usage which effectively changes the reset value of the 11th element of the COUNTERS array:

```

block slave {

register COUNTERS[256](COUNTERS[%d]) @'h0400 {

field value {

bits 32;

access ro;

reset 'h0;

}

change_reset COUNTERS[10] 'h1

}

```

The change\_reset property can also change the reset values of a field or field array through block or block instances also.

#### Example

The following example changes reset value of a field f which is inside register r2 which is instantiated inside block blk\_vh1 which is instantiated inside block blk\_vh:

```

register r2 {

...

field f

...

}

block blk_vh1 {

bytes 4

register r2 = r2[3]

...

}

block blk vh {

```

```

bytes 4

block blk_vh1 = blk_vh1

....

}

block blk3 {

bytes 4

register r2fields (pkt1)

register r1=r6 (reg_ar[%d])

register r1=r3 (reg_ar%d)

block blk_vh = blk_vh[2]

change_reset blk_vh[0].blk_vh1.r2[0].f 'b0

change_reset r6.f 'b0

change_reset r3 'b1

}

```

Following is the generated SystemVerilog code:

```

class ral_block_blk_val extends uvm_reg_block;

...

virtual function void build();

...

this.blk_vh[0].blk_vh1.r2[0].f.set_reset('b0);

this.r6.f.set_reset('b0);

this.r3.f.set_reset(32'b00000000000000000000000000000);

this.r3.f2.set_reset(32'b000000000000000000000000000);

endfunction : build

`uvm_object_utils(ral_block_blk_val) endclass :

ral_block_blk_val

```

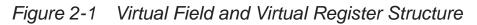

## **Virtual Fields and Virtual Registers**

By default, fields and registers are assumed to be implemented in individual, dedicated hardware structures with a constant and permanent physical location such as a set of D flip-flops. In contrast, virtual fields and virtual registers are implemented in memory or RAM. Their physical location and layout is created by an agreement between the hardware and the software, not by their physical implementation.

Virtual fields and registers can be modeled using RAL by creating a logical overlay on a RAL memory model that can then be accessed as if they are real physical fields and registers. The RAL model of the memory itself remains available for directly accessing the raw memory without regard to any virtual structure it may contain.

Virtual fields define continuous bits in one or more memory locations and can span a memory location boundary. Virtual fields are contained in virtual registers. Virtual registers define continuous whole memory locations. They can span multiple memory locations but are always composed of entire memory locations, not fractions of memory locations.

Virtual registers are always arrays because the usual reason they are virtual is that there are a large number of registers and implementing the registers in a RAM instead of individual flip-flops is most efficient. Arrays of virtual registers are associated with a memory. The association of a virtual register array with a memory can be static (for example, specified in the RALF file) or dynamic (for example, specified at runtime through your code). Static virtual registers are associated with a specific memory and are located at specific offsets within that memory. The association is specified in the RALF file and is created by the code generator. This association is permanent and cannot be broken at runtime.

#### Example 2-15 Static Virtual Register Array

```

block MAC {

...

memory DMABFRS { ... }

...

virtual register CHANNEL[1024] DMABFRS@0 {

field {...};

...

}

}

```

Dynamic virtual registers are dynamically associated with a userspecified memory and are located at user-specified offsets within that memory at runtime. The dynamic allocation of virtual register arrays can also be performed randomly by a Memory Allocation Manager instance. The structure of the virtual registers is specified in the RALF file, but the number of virtual registers in the array and its association with a memory is specified in the SystemVerilog or OpenVera code and must be correctly implemented by you. Dynamic virtual registers arrays can be relocated or resized at runtime.

Example 2-16 Dynamic Virtual Register Specification

```

block MAC {

...

memory DMABFRS { ... }

...

virtual register CHANNEL {

field {...};

...

}

}

```

Register and Memory Specification

Example 2-17 Implementing Dynamic Virtual Registers

Example 2-18 Randomly Implementing Dynamic Virtual Registers

Because virtual fields and virtual registers are implemented in memory, their content is not mirrored by the RAL model.

## **Multiple Physical Interfaces**

Some designs may have more than one physical interface, each with accessible registers or memories. Some registers or memories may even be accessible through more than one physical interfaces and be shared.

A physical interface is called a domain. Only blocks and systems can have domains. Domains contain registers and memories. If a block or system has only one physical interface, there is no need to specify a domain for that interface.

For example, the block "bridge" shown in Example 2-19 specifies a block with two physical interfaces and a register accessible from both interfaces at offset 0 in their respective address spaces.

Example 2-19 Specification for a Two-Domain Block

```

register xfer {

bytes 4;

field data {

access rw;

}

}

```

Feedback

Register and Memory Specification

```

shared (xfer_reg);

}

block bridge {

domain apb {

bytes 4;

register xfer;

}

domain ahb {

bytes 4;

register xfer;

}

}

```

Some physical interfaces may have different transactions used for configuration than the transactions used for normal operations. For example, PCI interfaces have configuration write transactions that are different from normal write transactions. Configuration transactions are typically used to set a base address and other decoding information required by normal transactions. Because configuration transactions are used separately from normal transactions, and normal transactions cannot occur until the DUT is suitably configured using configuration transactions, configuration and normal transactions on the same physical interface must be modelled as separate physical interfaces.

Systems with multiple domains can instantiate blocks with a single domain. A domain must be entirely instantiated within a system domain, that is, a block-level or subsystem-level domain cannot be split between two system-level domains. Different block-level or subsystem-level domains can be instantiated in the same systemlevel domain but in different address offsets. When instantiating a multiple-domain block or sub-system in a multiple-domain system, the same name and hdl\_path must be used for all instances. This creates a single instance of the block or subsystem with its various domains instantiated in different domains.

Example 2-20 shows a specification of a multiple-domain instantiation. Notice how the same instance name "br" and HDL path are used in both cases. Example 2-21 shows the corresponding abstraction model of the system. Notice how domains do not create an additional abstraction scope.

Example 2-20 Instantiating a Two-Domain Block in a Two-Domain System

```

system amba {

domain apb {

bytes 4;

block bridge.apb=br (amba_bus.bridge);

}

domain ahb {

bytes 4;

block bridge.ahb=br (amba_bus.bridge);

}

}

```

Example 2-21 Model of a Two-Domain Block in a Two-Domain System

```

class ral_block_bridge extends uvm_reg_block;

ral_reg_xfer xfer;

...

endclass

class ral_sys_amba extends uvm_reg_block;

ral_block_bridge br;

...

endclass

```

Example 2-22 Instantiating a Domain Array Block

block blk {

domain dom[8] {

...

Feedback

Register and Memory Specification

```

}

....

}

system sys {

domain sys_dom[8] {

bytes 4;

block blk.dom[*]=blk @'h1000;

...

}

...

}

```

## **Special Registers**

The UVM register library presumes all registers and memories are average registers and memories, they are accessible at a known, constant, unique physical address(es), their behavior is constant throughout the simulation regardless of the physical interface used to access them, and they contain a single value.

Special register behavior can be modeled using any number of extension capabilities provided in the UVM register and field abstraction classes. Pre- and post-read/write callback objects, virtual callback methods, user-defined front-doors, and user-defined back-doors may be used to extend the behavior of the base library.

This section discusses the following topics that are supported by UVM Ralgen:

- "Indirect Indexed Registers"

- "Unimplemented Registers"

- "Aliased Registers"

- "Banked Registers"

- "Shared Registers"

- "Sparse Register Arrays"

- "Modeling Non-Standard Behavior of Registers"

- "Accessing Registers Based on Index in a regfile"

#### **Indirect Indexed Registers**

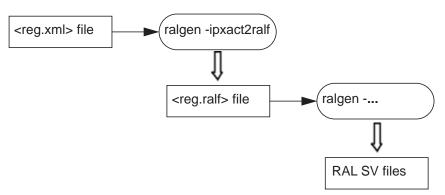

RALF provides support for indirect indexed registers. By default, the entire address space of registers and memories is assumed to be linearly mapped into the address space of the block that instantiates it. Each register or location in a memory corresponds to a unique address in the block.

However, some registers are not directly accessible through a dedicated address. Indirect access of an array of such registers is accomplished by first writing an "index" register with a value that specifies the array's offset, followed by a read or write of a "data" register to obtain or set the value for the register at that specified offset. This indexing mechanism allows to access a large memory in a limited address space.

In UVM-RAL, "data" register is modeled by extending the pre-defined uvm\_reg\_indirect\_data class. The "data" register must not contain any fields. The "index" and "array" registers must be built first, as "index" and "array" registers are specified when the "data" register is configured using the

uvm\_reg\_indirect\_data::configure() method. The indirect register array, "index", and "data" registers are added as members of the containing block.

Since the registers in indirect indexed register array are not accessible through dedicated addresses, they are not added to the map. Only, the "index" and "data" registers are added to a map in the containing block.

For details on indirect indexed registers, see section "Indirect Indexed Registers" in *Universal Verification Methodology (UVM)* 1.1 *User's Guide*.

The following is the specification for each of the three registers used for implementing UVM-RAL Indirect Indexed Register functionality:

#### • Indirect Index Register

Indirect Index register is specified like a regular register. It does not have a special syntax.

```

register idx_reg … {

…

}

```

#### • Indirect Array Register

Indirect Array register in UVM is not mapped to any address, hence the offset of an indirect array register needs to be mentioned as "none".

For example:

```

register array_reg @none {

field f1 {}

...

}

```

• Indirect Data Register

Indirect data register conveys the information regarding which registers are used as an index register and unmapped array register. You can use the "indirect\_data" property to provide this information. Also, an indirect data register should not contain any fields. An error message is issued if this register contains any fields.

In certain cases, you might have to index a group of registers that are essentially not register arrays. To index a non-array register, use the regfile instead of the register array as the regfile enables you to queue all the registers specified in the register file.

Inside the regfile, the regs queue property contains all the register handles present inside this regfile. The order of specification of register in the register file determines the index location and this queue is used to index each of the register specified inside.

Syntax for using indirect data registers:

```

indirect_data

<(indirect_reg[=arr_inst_name])|(indirect_regfile[=regf

ile_inst_name])> indirect_idx=idx_inst_name;

```

Example,

```

register r1 {

...

}

register r2 {

...

}

regfile rf {

register r1=r1 @none;

register r2=r2 @none;

}

```

Feedback

```

register ind {

field f {

bits 8;

}

}

system slave {

bytes 4;

block B1 @0 {

bytes 4;

reqfile rf=rf1 @none;

register ind=index @0x1;

register data1 @0x0 {

indirect_data rf=rf1 ind=index;

}

}

}

```

The generated SystemVerilog code includes the following configure call to use regs as indirect array:

```

this.datal.configure(this.index, this.rfl.regs, this,

null);

```

The Indirect Array and Indirect Index registers are extended from uvm\_reg class. However, the Indirect Data register is extended from the uvm\_reg\_indirect\_data class.

For example:

```

class ral_b1_data_reg extends uvm_reg_indirect_data.

...

endclass

```

The call to configure method involves specifying *Indirect Array* and *Indirect Index* instances:

data\_reg.configure(idx\_reg, array\_reg, this, null);

Apart from this, there is no mapping done for indirect array register.

#### Limitations

The following are the limitations with this feature:

- Indirect\_data rule is valid only while generating UVM code.

- An error is indicated if an Indirect data register contains any fields.

- Indirect array register must be an array.

- Indirect index register must be a non-array register.

#### Limitations with regfile

- The register file pointed should be specified as @none (unmapped). All the registers inside this register file should be unmapped (either unspecified or as @none).

- Different regfile instances cannot be used as both indirect indexed array and normal register file.

#### **Unimplemented Registers**